1 Memory Hierarchy In Modern Computer Architecture Download

1 Memory Hierarchy In Modern Computer Architecture Download A typical memory hierarchy. q take advantage of the principle of locality to present the user with as much memory as is available in the cheapest technology at the speed offered by the fastest technology. main memory (dram) secondary memory (disk) speed (%cycles): 1⁄2’s. size (bytes): 100’s. Memory hierarchy design. memory hierarchy design becomes more crucial with recent multi core processors: aggregate peak bandwidth grows with # cores: intel core i7 can generate two references per core per clock. four cores and 3.2 ghz clock. . 25.6 billion 64 bit data references second . .

Computer Memory Hierarchy And Its Characteristics Traditional Computer C sci 360 computer architecture 3 prof. stewart weiss the memory hierarchy decoders and multiplexers a decoder is a logic circuit that has an n bit input and 2n outputs. for each input combination exactly one output line is asserted. a multiplexer is a logic circuit that has n data inputs and log2 n selector inputs. the selector input lines. Facts: cpu needs sub nanosecond access to data to run instructions at full speed. fast storage (sub nanosecond) is small (100 1000 bytes) big storage (gigabytes) is slow (15 nanoseconds) huge storage (terabytes) is glacially slow (milliseconds). Number of misses * miss penalty =. = ic*(memory accesses instruction)*miss rate* miss penalty. hit rate ratio r = number of requests that are hits total number requests. miss rate = 1 – (hit rate) cost of memory access= rch (1 r) cm. ch is cost time from cache, cm is cost time when miss – fetch from memory. But then cache and memory would be inconsistent. write through: also update memory. but makes writes take longer. e.g., if base cpi = 1, 10% of instructions are stores, write to memory takes 100 cycles. effective cpi = 1 0.1×100 = 11. solution: write buffer. holds data waiting to be written to memory.

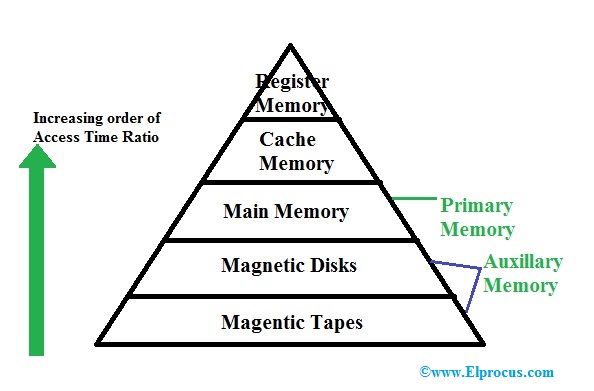

What Is Memory Hierarchy Definition Diagram Architecture And Advantages Number of misses * miss penalty =. = ic*(memory accesses instruction)*miss rate* miss penalty. hit rate ratio r = number of requests that are hits total number requests. miss rate = 1 – (hit rate) cost of memory access= rch (1 r) cm. ch is cost time from cache, cm is cost time when miss – fetch from memory. But then cache and memory would be inconsistent. write through: also update memory. but makes writes take longer. e.g., if base cpi = 1, 10% of instructions are stores, write to memory takes 100 cycles. effective cpi = 1 0.1×100 = 11. solution: write buffer. holds data waiting to be written to memory. Download scientific diagram | 1. memory hierarchy in modern computer architecture. from publication: chapter 5. realistic computer models | many real world applications involve storing and. Memory hierarchy. the cpu can only directly fetch instructions and data from cache memory, located directly on the processor chip. cache memory must be loaded in from the main system memory (the random access memory, or ram). ram however, only retains its contents when the power is on, so needs to be stored on more permanent storage.

Comments are closed.